# Power Analysis Based Side Channel Attack

Hasindu Gamaarachchi Harsha Ganegoda

arXiv:1801.00932v1

http://www.ce.pdn.ac.lk Department of Computer Engineering Faculty of Engineering University of Peradeniya Peradeniya 20200 Sri Lanka.

#### **Abstract**

Side channel attacks break the secret key of a cryptosystem using channels such as sound, heat, time and power consumption which are originally not intended to leak such information. Power analysis is a branch of side channel attacks where power consumption data is used as the side channel to attack the system. First using a device like an oscilloscope power traces are collected when the cryptographic device is doing the cryptographic operation. Then those traces are statistically analysesd using methods such as Correlation Power Analysis (CPA) to derive the secret key of the system. Being possible to break Advanced Encryption Standard (AES) in few minutes, power analysis attacks have become a serious security issue for cryptographic devices such as smart card.

As the first phase of our project, we build a testbed for doing research on power analysis attacks. Since power analysis is a practical type of attack in order to do any research, a testbed is the first requirement. Our testbed includes a PIC microcontroller based cryptographic device, power measuring circuits and a digital oscilloscope in the hardware side. In software side it includes algorithms running on the microcontroller, oscilloscope automation scripts and analysis programs. We verify the functionality of the testbed by attacking AES in time less than 10 minutes. Since building a test bed is a complicated process, having a pre-built testbed would save the time of future researchers.

The second phase of our project is to attack the latest cryptographic algorithm called *Speck* which has been released by National Security Agency (NSA) for use in embedded systems. So far, Speck has not been attacked using power analysis. In spite it has lot of differences to AES making impossible to directly use the power analysis approach used for AES, we introduce novel approaches to break Speck in less than an hour. Therefore, We practically show that even though the algorithm is very new still it is vulnerable to power analysis.

The third phase of the project is to work on countermeasures. After getting familiar with the current state of art, we select few already introduced countermeasures and practically attack them on our testbed to do a comparative analysis. Meanwhile, we try to form our own countermeasures and to improve existing countermeasures. Under circuit based countermeasures, the existing idea of implementing power line filters is practically implemented and tested. We show that it is not safe enough. We try few of our own circuit based ideas as well, to evaluate how good they are as countermeasures. But unfortunately none of them are good enough. Under software based countermeasures existing methods called random instruction injection and randomly shuffling Sboxes are implemented and tested. We show that those countermeasures are good enough for their simplicity and cost. But we identify the possible threat due to the problem of generating a good seed for the pseudo random algorithm running on the microcontroller. We address this issue by using a hardware based true random generator that amplifies a random electrical signal and samples to generate a proper seed.

# **Contents**

| 1 | Intr | oduction 1                                                |

|---|------|-----------------------------------------------------------|

|   | 1.1  | Cryptanalysis                                             |

|   | 1.2  | Side channel attacks                                      |

|   | 1.3  | Power analysis                                            |

|   | 1.4  | Power consumption of CMOS circuits                        |

|   | 1.5  | Power model                                               |

|   | 1.6  | Correlation Power Analysis (CPA)                          |

|   | 1.7  | Countermeasures                                           |

|   | 1.8  | The project and its objectives                            |

| 2 | Rela | nted work                                                 |

|   | 2.1  | Power analysis and Testbeds                               |

|   | 2.2  | Countermeasures                                           |

| 3 | The  | testbed 13                                                |

|   | 3.1  | Cryptographic device                                      |

|   |      | 3.1.1 AES on PIC microcontroller                          |

|   |      | 3.1.2 USB interfacing of the PIC and encountered problems |

|   | 3.2  | Power measurement circuit                                 |

|   |      | 3.2.1 Ground resistor method to measure power             |

|   |      | 3.2.2 $V_{DD}$ resistor method to measure power           |

|   |      | 3.2.3 The trigger for the oscilloscope                    |

|   | 3.3  | Construction of the PCB                                   |

|   | 3.4  | Power capturing automation                                |

|   | 3.5  | Summary                                                   |

| 4 | Atta | acking AES using CPA 24                                   |

|   | 4.1  | Steps of the attack                                       |

|   |      | 4.1.1 Generating plain text                               |

|   |      | 4.1.2 Selection function for AES                          |

|   |      | 4.1.3 Measuring power                                     |

|   |      | 4.1.4 Key derivation                                      |

|   | 4.2  | Number of traces                                          |

|   | 4.3  | Measuring circuit effect                                  |

|   | 4.4  | Noise filter effect                                       |

CONTENTS

| 5 | Spec | ck imple | ementation                                | 31       |

|---|------|----------|-------------------------------------------|----------|

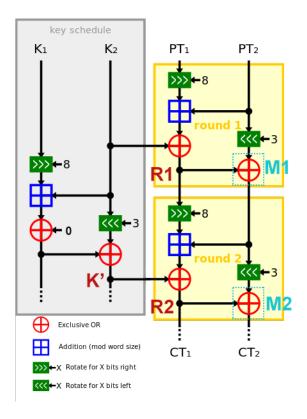

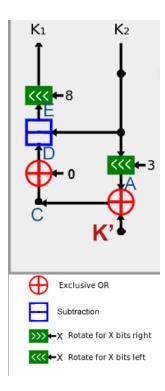

|   | 5.1  | Speck    | encryption algorithm                      | 31       |

|   |      | 5.1.1    | Operations in Speck                       | 31       |

|   |      | 5.1.2    | Variants of Speck                         | 31       |

|   |      | 5.1.3    | Steps in the algorithm                    | 31       |

|   | 5.2  | Differe  | ence with AES                             | 32       |

|   | 5.3  |          | for 8 bit                                 | 33       |

|   |      | 5.3.1    | ADD operation                             | 34       |

|   |      | 5.3.2    | ROTATE operation                          | 35       |

|   |      | 5.3.3    | XOR operation                             | 36       |

|   | 5.4  |          | d for Speck                               | 36       |

|   | 5.5  |          | for 16 bit                                | 37       |

|   | 5.5  | Speck    | 101 10 bit                                | 31       |

| 6 | Atta | ck on S  | peck                                      | 38       |

|   | 6.1  | Challe   | nge in attacking Speck                    | 38       |

|   |      | 6.1.1    | Difference in mixing the key              | 38       |

|   |      | 6.1.2    | Lack of sbox operations                   | 39       |

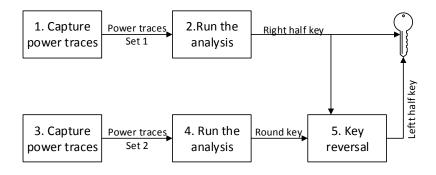

|   | 6.2  |          | to attack Speck                           | 39       |

|   | 6.3  |          | ences and difficulties                    | 41       |

|   | 0.5  | 6.3.1    | First attempt of the attack               | 42       |

|   |      | 6.3.2    | Zero key issue                            | 42       |

|   |      | 6.3.3    | The need of more number of traces         | 46       |

|   |      | 6.3.4    | Second attempt of the attack              | 47       |

|   | 6.4  |          | vulnerability                             | 48       |

|   | 6.5  |          | for 16 bit                                | 48       |

|   | 0.5  | Attack   | 101 10 bit                                | 40       |

| 7 | Circ | uit Cou  | intermeasures                             | 50       |

|   | 7.1  | filters  |                                           | 50       |

|   |      | 7.1.1    | Single capacitor                          | 51       |

|   |      | 7.1.2    | Single inductor                           | 52       |

|   |      | 7.1.3    | LC filter                                 | 53       |

|   |      | 7.1.4    | Effectiveness of tested filters           | 54       |

|   | 7.2  |          | ds we tried                               | 56       |

|   | ,    | 7.2.1    | Voltage regulator                         | 56       |

|   |      | 7.2.1    | Zener diode                               | 57       |

|   |      | 7.2.2    | Operational amplifier                     | 57       |

|   |      | 7.2.3    | Constant current source                   | 59       |

|   |      | 7.2.4    |                                           | 60       |

|   |      |          | An additional microcontroller in parallel |          |

|   |      | 7.2.6    | FTDI chip                                 | 62       |

|   |      | 7.2.7    | Effectiveness of tested methods           | 65       |

| 8 | Soft | ware co  | ountermeasures                            | 68       |

|   | 8.1  |          | m instructions                            | 68       |

|   | -    | 8.1.1    | Principles                                | 68       |

|   |      | 8.1.2    | Experiments and results                   | 69       |

|   | 8.2  |          | Shuffling                                 | 73       |

|   | 8.3  |          | vements                                   | 73<br>74 |

|   | 0.5  | 8.3.1    | Setup 1                                   | 75       |

|   |      | 8.3.2    | 1                                         | 73<br>78 |

|   |      | 0.5.4    | Setup 2                                   | 70       |

CONTENTS

| 9 | Con | clusion                   | 85 |

|---|-----|---------------------------|----|

|   | 9.1 | Testbed                   | 85 |

|   | 9.2 | Speck                     | 85 |

|   | 93  | Phase 3 · Countermeasures | 86 |

# **List of Figures**

| 1.1  | Side channel attack [1]                                                        | 2  |

|------|--------------------------------------------------------------------------------|----|

| 1.2  | Power analysis attack [2]                                                      | 3  |

| 1.3  | Dynamic power consumption during switching in a CMOS inverter [3, p. 32] .     | 4  |

| 1.4  | Classification of countermeasures                                              | 6  |

| 2.1  | A SASEBO board                                                                 | 9  |

| 3.1  | PIC programmer                                                                 | 14 |

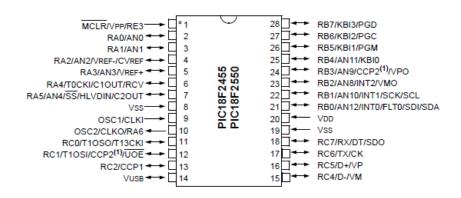

| 3.2  | Schematic diagram of PIC18F2550 from the datasheet                             | 14 |

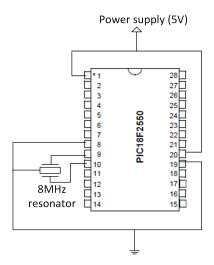

| 3.3  | Most basic circuit diagram for connecting the PIC                              | 15 |

| 3.4  | 8MHZ resonator                                                                 | 15 |

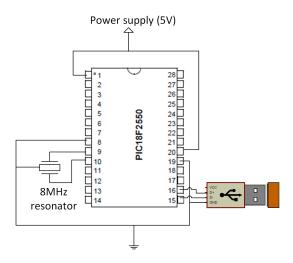

| 3.5  | Circuit after USB connection                                                   | 16 |

| 3.6  | 8MHz crystal                                                                   | 16 |

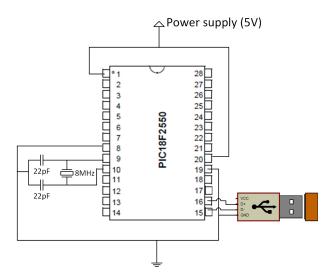

| 3.7  | Circuit after replacing the resonator with a crystal                           | 17 |

| 3.8  | Circuit after settling all USB errors                                          | 17 |

| 3.9  | Current drawn by a microcontroller                                             | 18 |

| 3.10 | Measuring power using ground resistor method                                   | 18 |

| 3.11 | Wrong way to ground the oscilloscope probe                                     | 19 |

| 3.12 | How the averaged power trace becomes 0 when oscilloscope ground is incor-      |    |

|      | rectly connected                                                               | 19 |

|      | Correct way to ground the oscilloscope                                         | 20 |

|      | A good averaged power trace                                                    | 20 |

|      | Measuring power using $V_{DD}$ resister method                                 | 21 |

|      | The cryptographic device and the power measurement setup on a breadboard .     | 22 |

|      | The cryptographic device and the power measurement setup on a PCB              | 22 |

| 3.18 | The overview of the basic steps in the automated power measurement setup       | 23 |

| 4.1  | Overview of AES [4]                                                            | 25 |

| 4.2  | The results printed by the CPA program                                         | 26 |

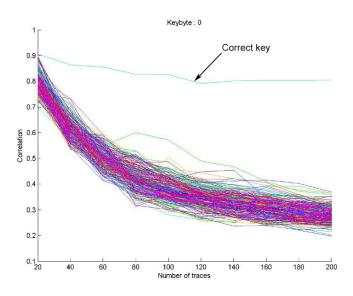

| 4.3  | Plot for keybyte 0                                                             | 27 |

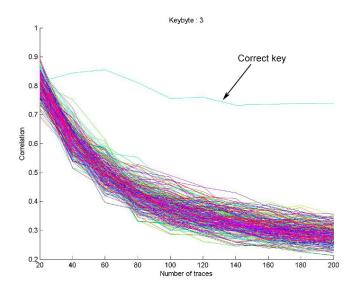

| 4.4  | Plot for keybyte 3                                                             | 28 |

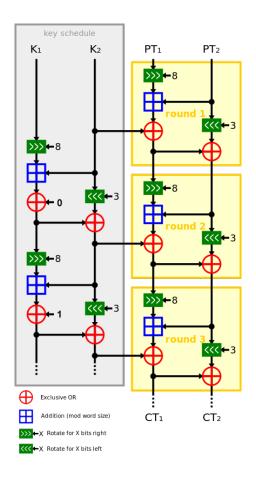

| 5.1  | Overview of Speck algorithm [5]                                                | 33 |

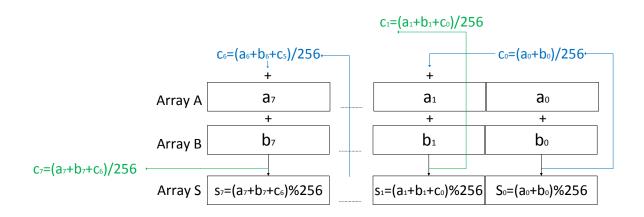

| 5.2  | Addition of 64 bit unsigned integers using a byte array                        | 34 |

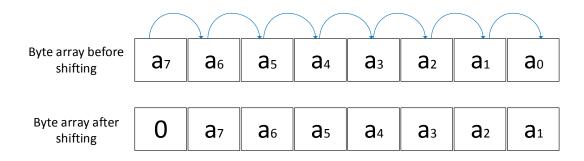

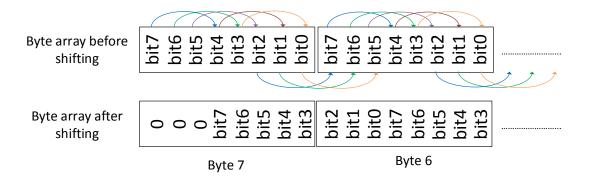

| 5.3  | An 8 bit shift right operation of a 64 bit unsigned integer using a byte array | 35 |

| 5.4  | bitwise right shift of a byte array by 3 bits                                  | 36 |

| 5.5  | Implementation of 3 bit right shift                                            | 36 |

| 5.6  | USB to RS232 TTL converter                                                     | 37 |

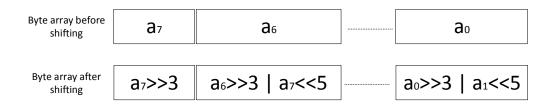

| 6.1  | Basic steps to attack Speck                                                    | 39 |

LIST OF FIGURES LIST OF FIGURES

| 6.2  | Power capturing points for Speck Speck                                                 | 40 |

|------|----------------------------------------------------------------------------------------|----|

| 6.3  | Deriving left half key from the round key                                              | 41 |

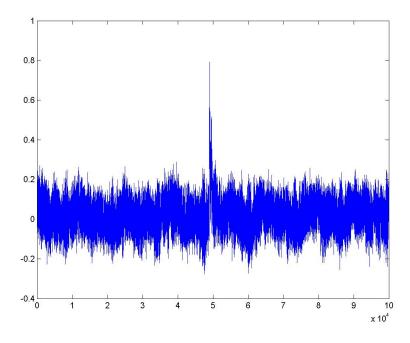

| 6.4  | The correlation vs time graph for a correct key when using <i>sbox</i> lookup as the   |    |

|      | selection function                                                                     | 43 |

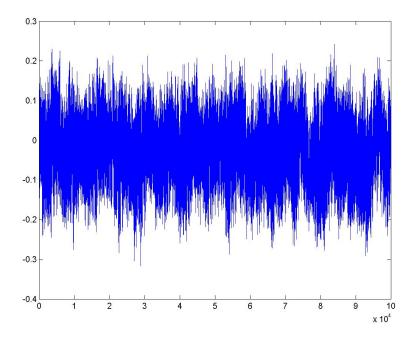

| 6.5  | The correlation vs time graph for a wrong key when using <i>sbox</i> as the selection  |    |

|      | function                                                                               | 44 |

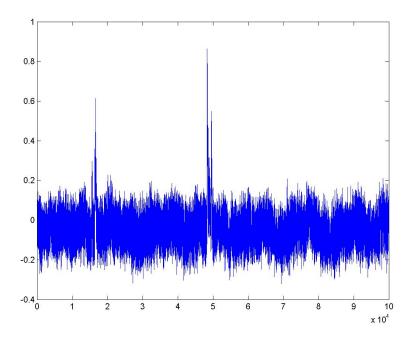

| 6.6  | The correlation vs time graph for a correct key when using <i>xor</i> as the selection |    |

| 0.0  | function                                                                               | 45 |

| 6.7  | The correlation vs time graph for the zero key guess when using <i>xor</i> as the      |    |

| 0.7  | selection function                                                                     | 45 |

|      | Selection function                                                                     | 73 |

| 7.1  | Single capacitor connected in parallel to the microcontroller                          | 51 |

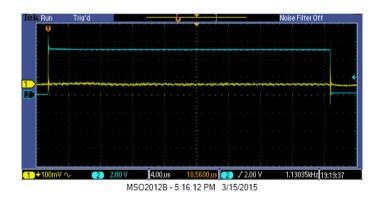

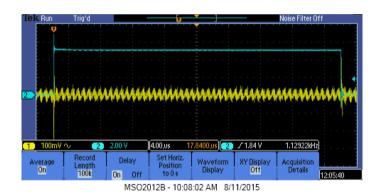

| 7.2  | Power trace when a capacitor filter is used                                            | 52 |

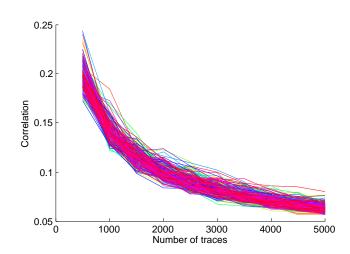

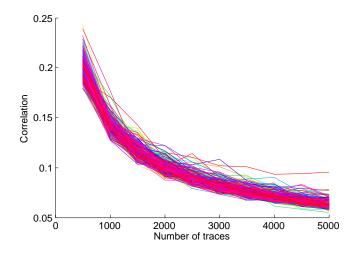

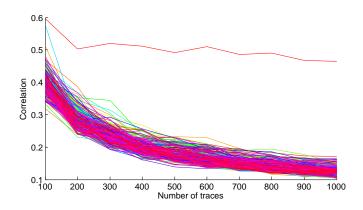

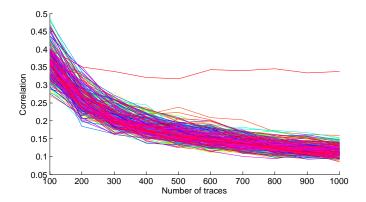

| 7.3  | Number of power traces needed when a capacitor filter is used                          | 52 |

| 7.4  | Single inductor connected serially to the microcontroller                              | 53 |

| 7.5  | Power trace when a inductor filter is used                                             | 53 |

| 7.6  | Number of power traces needed when an inductor filter is used                          | 54 |

| 7.7  | Providing power to the microcontroller through an LC filter                            | 54 |

| 7.8  | Power trace affected by a second order LC filter                                       | 55 |

| 7.9  | Number of power traces needed when an LC filter is used                                | 55 |

| 7.10 |                                                                                        | 56 |

| 7.11 | Power trace when a voltage regulator is used                                           | 57 |

|      | Connecting a reversed biased zener diode in parallel to the microcontroller            | 57 |

|      | Power trace when a zener diode is used                                                 | 58 |

|      | Number of power traces needed when a zener diode is used                               | 58 |

|      | Providing power to the microcontroller through an operational amplifier                | 59 |

|      | Power trace when a operational amplifier is used                                       | 59 |

|      | Number of power traces needed when an operational amplifier is used                    | 60 |

|      | Giving power through a constant current source                                         | 60 |

|      | Connecting another microcontroller in parallel                                         | 61 |

|      | Number of power traces needed when another microcontroller that write to the           | -  |

|      | serial port infinitely is connected in parallel to the power supply                    | 61 |

| 7.21 | Number of power traces needed when another microcontroller that do a mock              | -  |

|      | AES is connected in parallel to the power supply                                       | 62 |

| 7.22 | An averaged power trace on an Arduino Uno                                              | 62 |

|      | Hacking the Arduino Uno board for a successful power analysis attack                   | 63 |

|      | An averaged power trace on a hacked Arduino Uno                                        | 63 |

|      | An averaged power trace on an Arduino Mini Pro                                         | 64 |

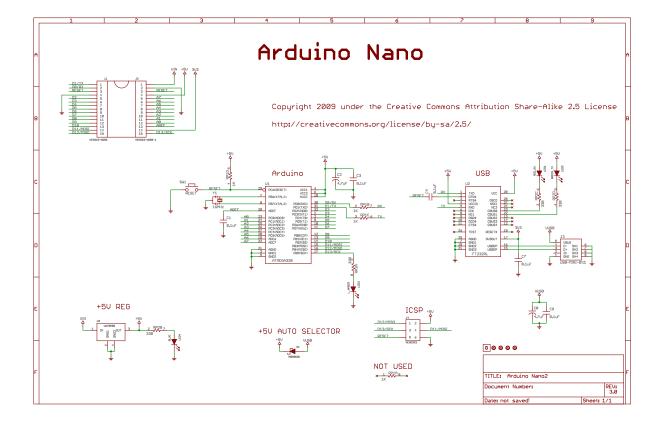

|      | Schematic of Arduino Nano [6]                                                          | 65 |

|      | Arduino Nano implemented on a breadboard                                               | 66 |

|      | FTDI chip connected in parallel to the microcontroller                                 | 66 |

|      | Averaged power trace when FTDI chip is connected in parallel to PIC2550                | 67 |

|      | Number of power traces required when FTDI chip is connected in parallel                | 67 |

| 7.50 | rumoer of power traces required when I I DI emp is connected in paramer                | 07 |

| 8.1  | Alignment requirement of power traces for a successful attack                          | 69 |

| 8.2  | How power traces are misaligned when a single random instruction is inserted.          | 70 |

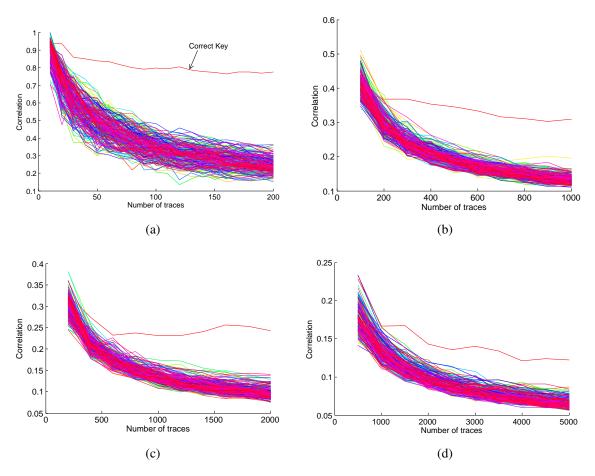

| 8.3  | The number of power traces required for injection of (a) no random instructions        |    |

|      | (b) one random instruction (c) Three random instructions (d) seven random in-          |    |

|      | structions                                                                             | 71 |

LIST OF FIGURES LIST OF FIGURES

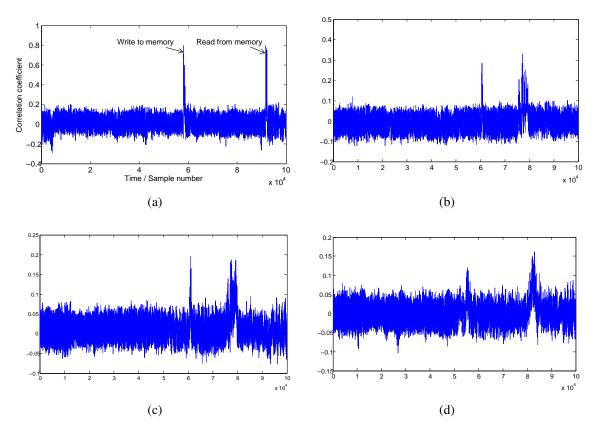

| 8.4  | Correlation peaks for injection of (a) no random instructions (b) one random      |    |

|------|-----------------------------------------------------------------------------------|----|

|      | instruction (c) Three random instructions (d) seven random instructions           | 72 |

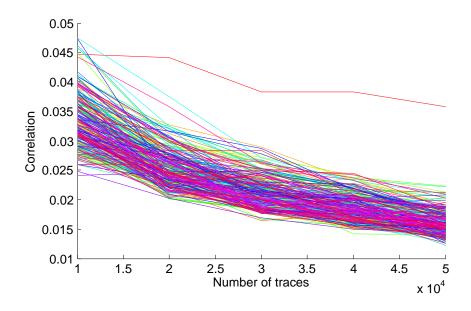

| 8.5  | Number of power traces required when Sbox operations are randomly shuffled .      | 74 |

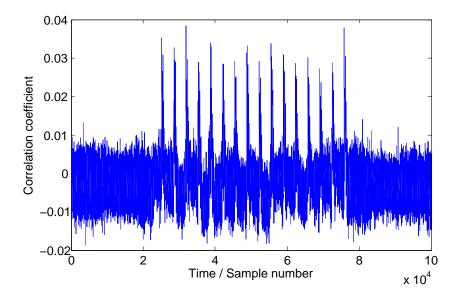

| 8.6  | Correlation peaks when SBox operations are randomly shuffled                      | 75 |

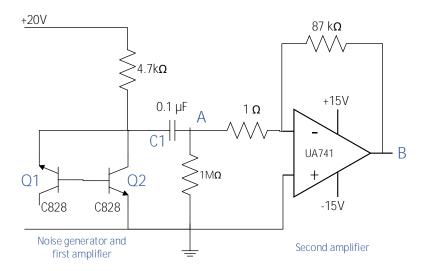

| 8.7  | Amplification of thermal noise via a resistor through an op amp caused saturation | 76 |

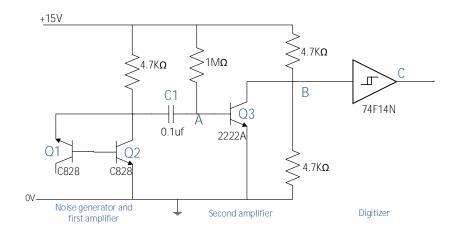

| 8.8  | Hardware random number generator that generates random pulses                     | 76 |

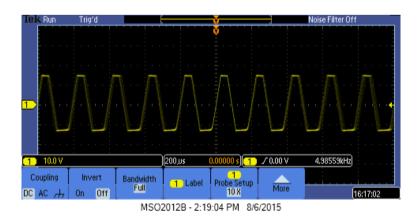

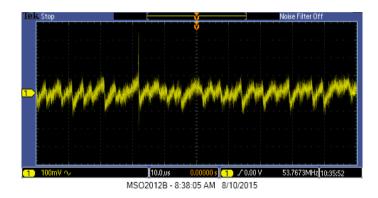

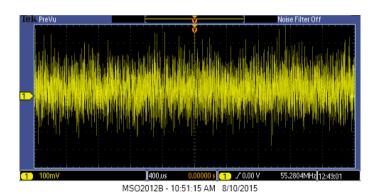

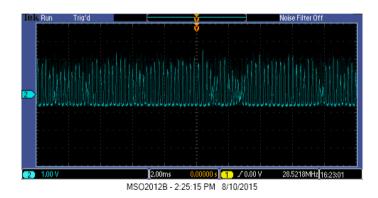

| 8.9  | Amplified reversed biased noise                                                   | 77 |

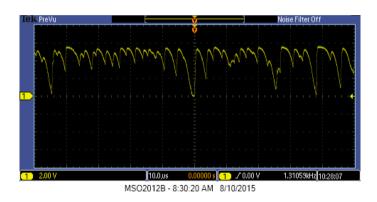

| 8.10 | Further amplified reversed biased noise                                           | 77 |

| 8.11 | Digitized random pulses                                                           | 78 |

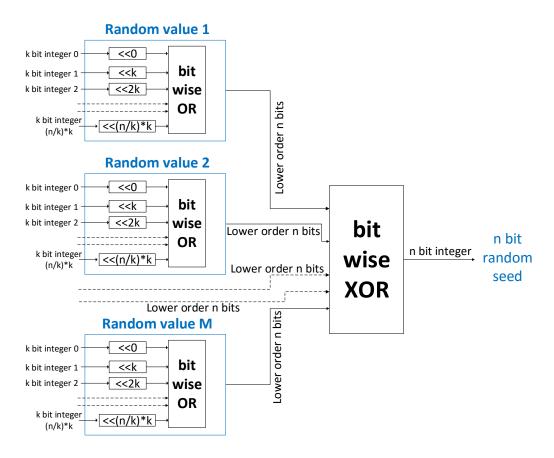

| 8.12 | The process of generating an n bit random seed using digitized random pulses .    | 79 |

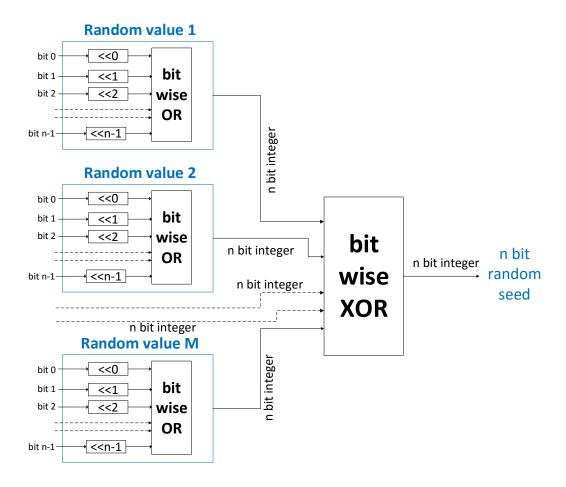

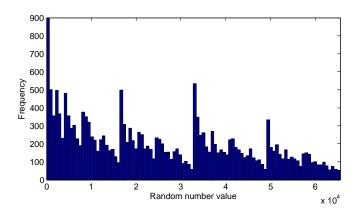

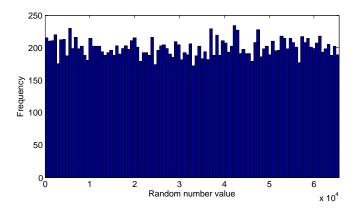

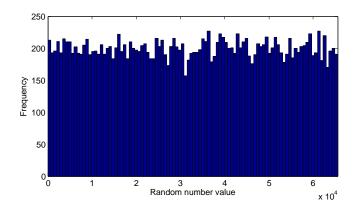

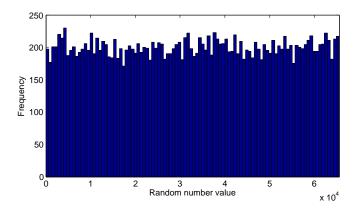

| 8.13 | Histogram for random numbers generated by xoring 100 values                       | 80 |

|      | Histogram for random numbers generated by xoring 1000 values                      | 80 |

| 8.15 | Histogram for random numbers generated by Matlab                                  | 80 |

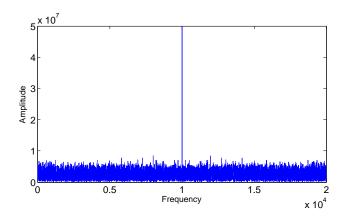

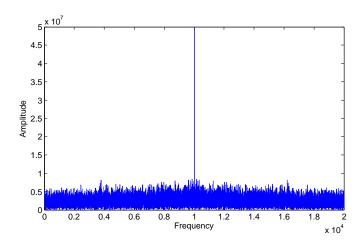

| 8.16 | Frequency spectrum of the signal formed by the hardware random number gen-        |    |

|      | erator                                                                            | 81 |

|      | Frequency spectrum of the signal formed by Matlab random number generator .       | 81 |

|      | Hardware random number generator that generates an analog waveform                | 81 |

|      | Amplified reversed biased noise                                                   | 82 |

|      | Further amplified reversed biased noise                                           | 82 |

| 8.21 | Process of generating a random seed via the analog to digital converter by sam-   |    |

|      | pling the amplified analog noise signal                                           | 83 |

|      | Histogram for random numbers generated by xoring 10 values                        | 84 |

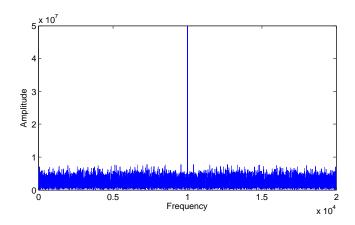

| 8.23 | Frequency spectrum of signal formed by generated random numbers                   | 84 |

# **List of Tables**

| 2.1                                           | Results for ground resistor method                                                                                            | 11                   |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 4.1<br>4.2<br>4.3<br>4.4                      | Results for 500 power traces                                                                                                  | 26<br>28<br>28<br>29 |

| 5.1<br>5.2                                    | Ten variants of Speck                                                                                                         | 32<br>34             |

| <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul> | The effect of the selection function on the difference between the the highest and the second highest correlation coefficient | 46<br>48<br>48       |

| 7.1<br>7.2                                    | Results for different filters                                                                                                 | 55<br>66             |

| 8.1                                           | Number of power traces and time required for different number of random instruction injections                                | 71                   |

# **Chapter 1**

# Introduction

Encryption is a process where a message is encoded such that it is only understandable by the intended parties. The input message known as the plain text is transformed to an output text known as cipher text using an encryption algorithm based on a parameter called the key. The cipher text must be again converted back to plain text is order to be read and this process known as decryption can be only done by a party who knows the secret key. Various encryption algorithms exist out there while AES (Advanced Encryption Standard), DES (Data Encryption Standard) and blowfish are some common examples.

## 1.1 Cryptanalysis

A cryptosystem is a pair of algorithms including the encryption algorithm and the decryption algorithm that does encryption and decryption based on a key. As the security of such a system fully depends on the secrecy of the secret key, if somehow the key is compromised then any unauthorized party will be able to decrypt the cipher text. Analysing a cryptosystem to find a weakness that would leak the secret key is called cryptanalysis [7]. Currently various attacks exist which can be used to derive the key of a cryptosystem in an unauthorized fashion.

The most trivial of such attacks is the brute force attack. In a brute force attack all the possibilities for the key are generated and are tried one by one until it matches the correct key. Brute force attacks fall into the category of traditional attacks. As modern encryption algorithms consist of very large keys as large as 128 bits or 256 bits, the number of permutations is huge that this type of attack is not practically feasible due to the huge computational time required. On the other hand another category of attacks called modern attacks exist which use mathematical approaches. Differential cryptanalysis and linear cryptanalysis are such methods and these methods are more effective than traditional attacks.

#### 1.2 Side channel attacks

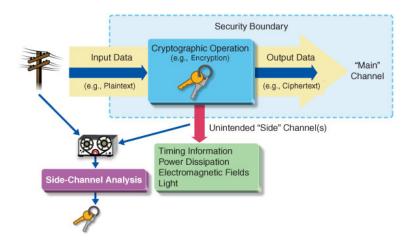

In addition to the two types of attacks described in section 1.1, now a very new type of attacks called side channel attacks have become popular [8]. These attacks use the weakness in the physical implementation of the cryptosystem to derive the secret key. For example a system can give out sound, heat, light or other electromagnetic radiation when under operation. These usually can have a relationship with what is happening inside a system and an attacker can make use of those things to determine the secrets inside a system. Such channels that leak

out information are called side channel attacks. If these side channels are used to attack a cryptosystem then they are called side channel attacks.

Figure 1.1: Side channel attack [1]

Consider Figure 1.1. Plain text is given as input to the system and the system runs the encryption to output cipher text. The key used in the system is unknown to the outside. But the system leaks out information using various side channels unintendedly. These side channel data are collected and they are analysed together with the input data to derive the secret key. This same process can be done in an decryption operation as well where now the input would be cipher text and output would be plain text.

#### 1.3 Power analysis

Power analysis is a branch of side channel attacks where the side channel used is the power consumption. In electronic devices, the instantaneous power consumption is dependent on the data that is being processed in the device as well as the operation performed by that device [3, pp. 6-12]. Therefore by analysing the power consumed by a device when it is doing encryption or decryption the key can be deduced.

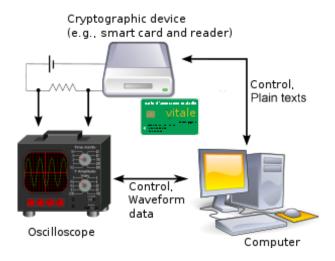

Consider Figure 1.2. The computer inputs a set of known plain texts to the cryptographic device which does the encryption. While the device performs the encryption the oscilloscope measures the power consumptions. For several hundreds of plain text samples power traces are obtained and then they are analysed on a computer using an algorithm such as Simple Power Analysis (SPA), Differential Power Analysis (DPA) [9] or Correlation Power Analysis (CPA) [10] to derive the secret key of the system. As the plain text in this case is known to the attacker this is a known plain text attacks.

## 1.4 Power consumption of CMOS circuits

CMOS circuits are made up of pairs of p type and n type MOSFET (Metal Oxide Semiconductor Field Effect Transistors). Microprocessors, microcontrollers, static RAM and many other digital logic circuits in the modern world use CMOS (Complementary Metal Oxide Semiconductor) technology. Therefore for power analysis which involves power consumption of a cryptographic device, focusing on power consumption of CMOS circuits is important.

Figure 1.2: Power analysis attack [2]

Instantaneous power consumption of a circuit is given by the following equation. Here p is the instantaneous power, v is the instantaneous voltage and i is the instantaneous current.

$$p = vi$$

As the voltage given to a circuit is equal to the power supply voltage and because it is always constant, the above equation can be now written as follows. Here  $V_{DD}$  is the voltage of the power supply. Therefore by measuring the instantaneous current, the instantaneous power consumption can be deduced.

$$p = V_{DD}i$$

The power consumption of a CMOS circuits is made up of two components as static power and dynamic power. Static power is due to the leakage current of transistors and therefore it is dependent on the design of the circuit. On the other hand, dynamic power is due to the switching of transistors and therefore it is dependent on the data being processed and the operation being done. As power analysis utilizes the relationship between power consumption and the data being processed, dynamic power is the relevant one. As the static power is mostly constant, the variation in the total power is solely due to dynamic power and therefore the total power consumption can be directly used for an attack.

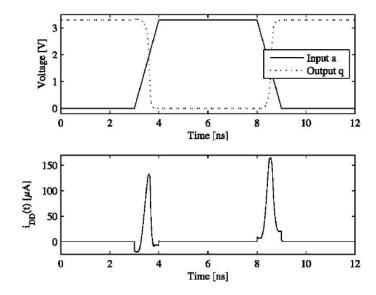

Dynamic power is consumed when switching occurs in transistors. That is if a CMOS cell changes from 0 to 1 or from 1 to 0, switching occurs in transistors and power is consumed. Figure 1.3 is for a CMOS inverter. Upper graph there shows the input signal and the output signal of the CMOS inverter while the below graph shows the instantaneous current. As you can see there are two transitions in the input signal where at first it goes from 0 to 1 and then from 1 to 0. At these moments where switching takes place peaks are visible in the instantaneous current drawn by the circuit.

These clear changes in the current is due to the current drawn to charge the capacitance in the transistors and the temporary short circuit current that is drawn during switching. In devices such as a microcontrollers, the data bus which is long and connected to many components have a quite big capacitance. Therefore writing to the data bus during a memory read or write causes a significant power consumption. When attacking software based encryption using power analysis this is the point which is mostly made use of.

Figure 1.3: Dynamic power consumption during switching in a CMOS inverter [3, p. 32]

#### 1.5 Power model

A power model is used to deduce the power consumption of a circuit mathematically using the information we have about the circuit. Hamming distance model is a very simple such power model. Even though it is not the most accurate, for our cause it is quite suitable.

In the data bus explained in section 1.4 if the initial value on the bus was v0 and the value after the change is v1 then the hamming distance can be simply found by counting the number of 0 to 1 and 1 to 0 transitions that happen. If the data bus is four bits and if v0 = 1010 and v1 = 0011 only two bits have changed (first and the last) and therefore the hamming distance is equal to 2.

The hamming distance between two values v0 and v1 can be calculated by the following equation where HD stands for Hamming Distance and HW stands for Hamming Weight. Hamming weight is the number of bits which are equal to 1.

$$HD(v0, v1) = HW(v0 \ XOR \ v1)$$

As the significant power consumption in the CMOS circuit occurs during transitions, this model works fine. Most microcontrollers usually set the data bus to 0 or 1 before writing a value to it. In a data bus where all the bits are set to 0 first, hamming distance is just the hamming weight of the value written to the bus afterwards(  $HW(v\ XOR\ 0) = HW(v)$ ). If it is a data bus where all bits are initially set to 1 then the hamming distance is equal to hamming weight of the value written subtracted by the number of bits in the bus. (  $HW(v\ XOR\ 1) = Num\_bits - HW(v)$ ). Therefore for most microcontrollers hamming weight can be directly used as the power model.

## 1.6 Correlation Power Analysis (CPA)

Correlation Power Analysis (CPA) as mentioned above is an algorithm used to do power analysis. It is a statistical type of attack and uses the Pearson correlation coefficient to correlate

data. CPA is more recent and when compared to other algorithms such as DPA has numerous advantages such as requirement of less number of power traces [10].

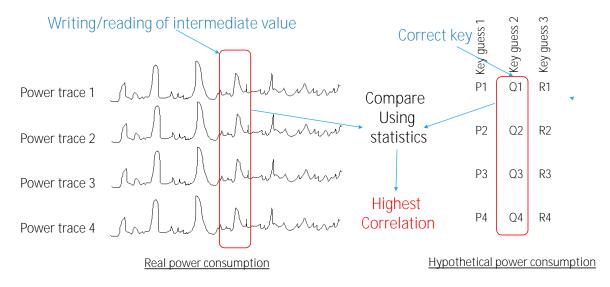

As the first step of the attack, an intermediate value generated during the cryptographic operation (encryption or decryption) which is a function of a variable data value and part of the key must be selected. This function is known as the selection function. In the equation below I is the intermediate value. The variable data sample which is generally plain text or cipher text is shown by d. k is part of the key which will be called as the subkey after this point.

$$I = f(d, k)$$

Then power measurements must be done when the device is doing the cryptographic operation. Here power traces must be obtained for several hundred (or thousands depending on the system) of samples for d. These obtained traces are the real power consumption values. Imagine that we used N number of plain text samples to get N number of power traces. Each power trace would have M number of sampling points which correspond to power consumption at each sampled moment in time.

After that, the intermediate values for each of the variable data samples used and the power consumption for those intermediate values must be calculated using a power model such as hamming distance model. This calculation must be repeated for all possible values for the subkey considered. These calculated data are the hypothetical power consumption values.

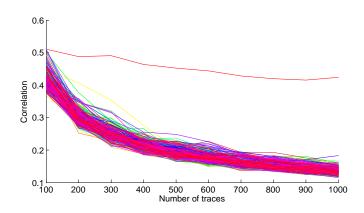

Finally the real power consumption values and the hypothetical power consumption values per each subkey must be compared to each other to find out which subkey has the highest correlation. This comparison is done using the statistical method called Pearson correlation coefficient given by the equation below [10]. In the equation, the  $j^{th}$  sample point of the  $i^{th}$  power trace has been written as  $W_{i,j}$ . The hypothetical power consumption value for the  $i^{th}$  plain text (or cipher text) with respect to the appropriate subkey has been written as  $H_i$ . An estimate for the correlation for  $j^{th}$  sampling point for a certain subkey can be found using the equation.

$$\hat{\rho} = \frac{N \sum_{i=0}^{N} W_{i,j} H_i - \sum_{i=0}^{N} W_{i,j} \sum_{i=0}^{N} H_i}{\sqrt{N \sum_{i=0}^{N} W_{i,j}^2 - (\sum_{i=0}^{N} W_{i,j})^2} \sqrt{N \sum_{i=0}^{N} H_i^2 - (\sum_{i=0}^{N} H_i)^2}}$$

Pearson correlation coefficient is a value between -1 and 1. If the value is 1 that means the two data sets compared (hypothetical power consumption values and real power consumption values) have the best correlation. If 0 that means there is no correlation at all. -1 means they are correlated at best but the relationship is such that the values in the data sets are inversely proportional. As the two data sets used here to find the correlation coefficient is the hypothetical power consumption data and the real power consumption data, the correlation coefficient depicts how much they are related. Therefore the maximum correlation coefficient would be obtained when the hypothetical power consumption values for the samples are calculated using the correct key.

The fact that the analysis is done separately on separate subkeys is the one that reduces the complexity of a correlation power analysis attack to a practically feasible value. For example consider a 128 bit key. A 128 bit key has 2<sup>128</sup> possibilities and checking such number of possibilities is not feasible even on a super computer. This is why a brute force approach is not feasible for most encryption algorithms out there today. Now consider a CPA attack where a subkey is size of a byte. Here the 128 bit key is divided into 8 bit portions to make 16 bytes. A byte which is 8 bits just have 256 possibilities and when all 16 keybytes are considered only 256x16 possibilities must be computed. This number of computations is practically feasible.

#### 1.7 Countermeasures against power analysis attacks

Countermeasures are the techniques that are implemented with the ultimate goal of preventing power analysis attacks. But unfortunately in the security world there are no such hundred percent perfect countermeasures. Therefore the objective of a countermeasure against power analysis is to make an attack extremely difficult. When the time and the cost for an attack is large enough such that it would be infeasible for an attacker, such a countermeasure can be considered good enough.

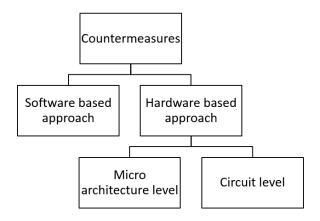

Figure 1.4: Classification of countermeasures

Countermeasures against power analysis attacks can be categorized in to two broad categories as hardware based countermeasures and software based countermeasures as shown in Figure 1.4. Hardware based countermeasures as the names suggests is the addition of new components or modification of existing components of the cryptosystem, in order to minimize the leakage of secret data as power. Hardware countermeasures can be further classified into two categories namely circuit level countermeasures and micro architecture level countermeasures as shown in Figure 1.4. Circuit level countermeasures involve addition of components to the circuit or modification of the circuit at a macro level. For example adding a power line filter to the cryptographic device or connecting a noise source are circuit level countermeasures. Micro architecture level countermeasures involve addition of components or modification of components at logic gate level. For example, adding additional transistors to a CMOS gate such that power consumption becomes different, is such micro architecture level countermeasure. Software based countermeasures on the other hand do modifications to the program code that runs on the microcontroller of the cryptographic device. For example inserting some false instructions randomly at the middle of the encryption to change the power consumption pattern is a software based countermeasure.

Due to the massive threat imposed by power analysis attacks, a lot of research is already conducted to form various countermeasures. Currently there are many such introduced countermeasures and are elaborated in chapter 2.

## 1.8 The project and its objectives

Embedded cryptographic devices such as smart cards are very much vulnerable to power analysis attacks [3, pp. 1-5]. For example, the key of certain smart cards can be obtained in a small amount of time as 90 minutes by devising a power analysis attack [11]. Embedded devices such

as smart cards are widely used for authentication mechanisms. Further even ATM (Automated Teller Machine) cards and SIM (Subscriber Identity Module) cards are also smart cards. Therefore as this type of attacks are a serious risk for the security, researchers are proposing various countermeasures.

To find countermeasures or do any other power analysis based research on the first place a testbed is needed. That is a system comprising of a cryptosystem, power measurement system and necessary software to do the analysis is needed. Building such a system involves a difficult process which is time consuming. While it needs a quite good knowledge on electronics, computer interfacing, mathematics and programming knowledge, the process needs spending lot of time to do troubleshooting. Anyone who is interested in power analysis going through this same process is a wastage of time. But if a testbed is already available one can directly start on countermeasures or similar research rather than going through the troubles of building the testbed. Moreover if such an already built system is available anyone who has a little electronic knowledge also can use it.

The first phase of our project is to build such a testbed for power analysis based side channel attacks. As described before, the objective is to help researchers who are interested on countermeasures to save them from the testbed setup time and difficultly. And also we need this testbed to continue the next phases of the projects for this semester as well as the next semester. The cryptographic device of the testbed is built using a reprogrammable microcontroller such as PIC or AVR. Therefore this device does software based encryption opposed to hardware based encryption which in that case uses direct logic circuits or FPGA (Field Programmable Gate Array). Then we attack AES using the created testbed to check whether our testbed works properly.

The second phase is to do cryptanalysis on an encryption algorithm called Speck. Speck is a very recent encryption algorithm that was released by the NSA in June 2013. This belongs to the type of ciphers called block ciphers which AES also belongs, but the speciality is this is a very lightweight cipher targeted mainly for embedded systems. Therefore it is expected to be famous among embedded devices in the future and therefore it must be tested to check whether this algorithm is vulnerable to power analysis to determine the necessity of countermeasures. Up to now according to best of our knowledge there is no such power analysis based cryptanalysis done on Speck. Therefore in the second phases we check whether Speck is vulnerable to power analysis attacks. This phase also involves implementation of Speck for 8 bit microcontrollers, due to the fact that such an implementation currently is not available.

Currently there is a lot of available countermeasures against power analysis as we explain in chapter 2. But at one point any of them would fail. Performance and powerfulness of computers as well as devices such as digital oscilloscopes are rapidly increasing and therefore the effectiveness of old countermeasures decrease. A countermeasure which appears to take infeasible amount of time to be attacked today might become feasible in the future with the improvement of technology. Further, the effectiveness of a countermeasure would compromise factors such as power, performance, device size and cost. For example adding new hardware components will increase power consumption and the device size, which is not preferred. Integrating a software countermeasure would reduce the performance and efficiency. Meanwhile any countermeasure would definitely increase the cost of a cryptographic device. Due to all these reasons countermeasures against power analysis is still a very open research area. Therefore the third phase of our project is to work on countermeasures against power analysis. First we study the current state of the art of hardware based countermeasures. Then we would practically test some selected circuit based countermeasures on the testbed we have created and evaluate their effectiveness. Here we limit testing of hardware based countermeasures only to circuit based

countermeasures as micro architecture level ones would need access to advanced facilities such as fabrication. Next we study the current state of art of software countermeasures and then some selected software countermeasures would be tested and evaluated. Finally we improve a selected countermeasure with the goal of contributing towards the security of embedded devices. Meanwhile we would also test some new ideas to verify whether they are good enough as countermeasures or not.

The rest of the report is organized as follows. In chapter 2 we discuss about the related work. In chapter 3 we discuss the process of building of the testbed and in chapter 4 we discuss how AES algorithm was attacked and its results. Then in chapter 5 how the implementation of Speck algorithm for PIC was done is explained. In chapter 6 the attack on Speck is discussed while emphasizing the new approaches and mechanisms needed while presenting the results. In chapter 7 we elaborate some selected circuit based countermeasures and present the results from the tests we did for verifying their effectiveness. Several new circuit based ideas tested by us are also presented with evaluation results on their performance. In chapter 8 we elaborate some selected software based countermeasures and show how effective they are, based on the test we carry out. Improvements done by us to a selected software based countermeasure is also elaborated. Finally we conclude the report in chapter 9.

# Chapter 2

## **Related work**

#### 2.1 Power analysis and Testbeds

National Institute of Advanced Industrial Science and Technology in Japan has produced a side channel attack evaluation board called SASEBO board for power analysis [12]. The image of a board is shown in Figure 2.1.

Figure 2.1: A SASEBO board

This is a commercially available board but this being built using an FPGA does hardware based encryption. Power analysis on hardware based encryption and software based encryption has differences and therefore for those who do research on software based encryption this board cannot be used. On the other hand most cryptodevices such as smart cards use microcontrollers in their design due to the low cost and hence that is software based encryption. The cryptographic device of our testbed does software based encryption and therefore it would be useful for anyone interested in software based encryption.

Martinasek et al. [13] has created a testbed for Differential Power Analysis where the cryptographic device is based on a PIC microcontroller. But the method they have used to interface the cryptographic device to the computer is RS232. Today most computers such as laptops does not have RS232 interfaces and therefore using it with such a computer is not straight forward. In our setup we have interfaced the cryptographic device using Universal Serial Bus (USB) and because almost all computers today are equipped with USB ports our device can be more easily used. Further for measuring power they have used a current probe. A current probe is much costly and our laboratory does not have such probes. On the other hand our power measurement setup measures voltage rather than the current and therefore ordinary oscilloscope probes can be used.

Petrvalsky et al. [14] has created the cryptographic device for their testbed using an 8051 based processor for Differential Power Analysis. They have used a USART for communication and again the use of RS-232 causes the problems discussed in the previous work. To measure power they use two different setups. One method is for ordinary oscilloscope probes while the other method is for differential probes which are costly. They claim that the method that does not use differential probes require more power traces to derive the key than the method that use differential probes. In our work we introduce a new power measurement method that uses ordinary probes but yet needs similar number of traces the method that used the differential probe required. This power measurement method is not found in any publication available to us.

Petrvalsky et al. [15] has also created a testbed based on an ARM based processor and there as well the same USART have been used. In this setup for power measurement a differential probe is required. This type of probes are much costly than an ordinary oscilloscope and they are not available in our lab. Our power measurement setup as described above uses ordinary oscilloscope probes. They have alternately suggested a method to use two ordinary oscilloscope probes instead of the differential probe but then with another probe for the trigger a total of three probes are needed. Oscilloscopes normally come with two probes and even if three probes were available then the waves from the first probe has to be subtracted from the second one which produces an unnecessary overhead. Our power measurement setup only require two probes, one for power measurement and the other for the trigger.

Tepanek et al. [11] designed an AVR microcontroller based power analysis testbed and the cost for the testbed including the testbed is claimed to be \$2300. The upper margin of their oscilloscope at that time is \$2000 and therefore the cost for the cryptographic device with the power measurement circuits and relevant interfacing circuits is about \$300. This is a bit higher cost for us and therefore we have come up with a setup which is less costly than that. Another issue in this setup as similar to the previous ones is the use of serial port for interfacing.

Moreover all the publications above that discuss power analysis on software based encryption does not discuss any detailed information about the testbed they have created. They neither include any steps or the methodology they followed in building the testbed. Therefore those testbeds are not easily reproducible.

Another issue with the above mentioned publications is that they all use AES to do power analysis. Apart from them there are many other works related to power analysis but they are also mostly about AES or DES. According to best of our knowledge currently there is no work that discuss about power analysis on the Speck algorithm. Therefore the fact that whether the algorithm is vulnerable to power analysis attacks is yet unknown. In the second phase of our project we do power analysis on Speck.

Brier et al. [10] introduced the Correlation Power Analysis algorithm for analysing the power traces to derive the secret key. As explained in section 1.6 we make use of this algorithm for the power analysis attack.

Correlation Power Analysis algorithm has a large time complexity and hence a generic implementation that runs on the CPU takes a considerable amount of time. This makes it difficult due to the fact that large amount of time has to be waited to get the result for an attack. Therefore we use an implementation of Correlation Power Analysis on CUDA (Compute Unified Device Architecture) done for a previous project during semester 5 which harness the power of thousands of threads in NVIDIA GPUs to accelerate the algorithm more than 1000 times faster [16]. As that implementation was for analysing power traces for hardware based encryption, couple of changes were done to port it for software based encryption. As this was for attacking AES for the attack on Speck it has to be further modified to comply with that algorithm.

| Method                              | Introduced by      | Issues                         |  |  |  |

|-------------------------------------|--------------------|--------------------------------|--|--|--|

| Injecting dummy instructions        | Kocher et al. [9]  | Cannot prevent SPA             |  |  |  |

| Injecting valid instructions        | Ambrose et al.     | Decreased performance          |  |  |  |

|                                     | [19]               |                                |  |  |  |

| Randomly shuffling Sbox opera-      | Mangard et al. [3] | Limited by the number of       |  |  |  |

| tions                               |                    | Sboxes                         |  |  |  |

| Dividing the standard Sbox into two | Goubin and         | Susceptible to 2nd-order DPA   |  |  |  |

| different Sbox                      | Patarin [20]       |                                |  |  |  |

| Software balancing by processing    | Daemenand and      | Susceptible to signal process- |  |  |  |

| words containing both the data bits | Rijmen [21]        | ing analysis                   |  |  |  |

| and their complements               |                    |                                |  |  |  |

| Doubling the data width, to include | Arora et al. [22]  | Increased power consumption    |  |  |  |

| both the original data and its com- |                    |                                |  |  |  |

| plementary value                    |                    |                                |  |  |  |

Table 2.1: Results for ground resistor method

#### 2.2 Countermeasures

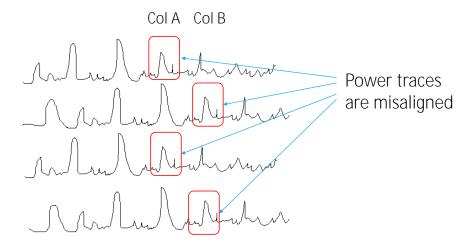

Work related to circuit level hardware countermeasures are very few. Sprunk [17] in his invention uses a clock that outputs a stream of random clock pulses. When the clock is unpredictable, the moment at which a certain instruction would run is also unpredictable. Therefore the obtained power traces would be misaligned. The misalignment of power traces makes it necessary to collect and analyse large number of power traces which makes the attack more time consuming. But many communication protocols such as USB and RS232 need a stable clock and therefore usage of an unpredictable clock is a disadvantage is such situations.

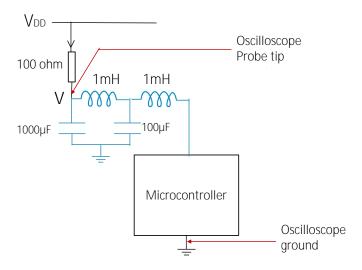

Kocher et al. [9] proposed introducing noise to the power line which is also a circuit level countermeasure. When noise is manually added using some noise generating device, it decreases the signal to noise ratio (SNR) and hence the number of required power traces increase. Mangard [3, pp. 167-175] also proposed several circuit level countermeasures. One technique is filtering the power line. When an appropriate filter is connected to the cryptographic device, the exploitable power consumption patterns are attenuated making the attack difficult. Mangard [3, pp. 167-175] also proposed skipping clock pulses. When the clock signal is passed through a filter which randomly skips clock pulses, the alignment of the power traces are broken making the attack difficult. According to best of our knowledge, most of these countermeasures are just proposed but not practically tested. Therefore we practically implement some of these countermeasures and attack them to check how effective they are.

On the other hand there are lot of work regarding micro architecture level hardware countermeasures. For example Waddle and Wagner [18] introduced a method called dual rail logic to achieve constant power consumption for every clock cycle. This eliminate the correlation between power traces and the data and operation being processed. But devices with micro architecture level countermeasures are very costly. Also the power is consumed equally all the time increasing the power consumption. Further additional logic gates increases the device size as well. Working on micro architecture level countermeasures would need technologies such as fabrication and hence we are not focusing on these countermeasures.

On software countermeasures as well there are a lot of works. Table 2.1 work summarizes some selected software based countermeasures.

In dummy instruction injection method, instructions such as NOP (No Operation) are randomly inserted to the encryption code. This breaks the alignment of power traces and hence the number of power traces required for the attack increases. But NOP instructions which do not do any work would have a power consumption pattern that is easily distinguishable. Therefore using techniques such as SPA the traces can be visually inspected to detect the NOPs.

The method proposed by Ambrose et al. [19] inserts real instructions instead of NOPs. This makes visual inspection of power traces a challenge. But inserting extra instructions is a compromise with power consumption. But random instruction insertion is quite simple to implement on any microcontroller. Therefore this method is less costly and easily feasible but yet provides considerable level of security when compared many other countermeasures. But the effectiveness of the countermeasure has been only tested on a simulator. In simulators ideal conditions are assumed when modeling the real systems. But in real systems such ideal conditions do not exist and hence the effects may be different, Therefore we practically implement the random instruction insertion countermeasure on our testbed and attack it to evaluate the effectiveness on a real system.

The method called randomly shuffling Sbox operations introduced at [3] proposes to randomly change the order at which is the Sbox operations are done. Since the number of Sboxes in an algorithm is limited, the number of required power traces cannot be indefinitely increased like in random instruction injection. But as no additional operations are performed unnecessary computations and power consumption do not happen. We test this countermeasure as well, in our testbed.

# Chapter 3

# The testbed

As discussed in the introduction to do any power analysis attack research first of all a testbed is needed. Creating the testbed was a great challenge as any source that properly explained the steps in a systematic fashion could not be found. It was more challenging as it required knowledge in various areas such as microcontroller programming, oscilloscope automation, microcontroller interfacing and electronics where they had to be explored and learnt. Further, lot of failures occurred when building the system and there was no proper source that explained the steps to troubleshoot and therefore most problems were solved mostly by experimentation. In this chapter we discuss the methodology that was followed in constructing the testbed while elaborating the difficulties encountered and how they were solved. The testbed construction has been divided into the following sections although they are tightly combined, for the convenience of proceeding the explanation.

## 3.1 Cryptographic device

#### 3.1.1 **AES on PIC microcontroller**

Cryptographic device is responsible for carrying out the cryptographic operation which is encryption, decryption or both. This device mimics the real device under attack such as a smart card, but for power analysis research as various modifications are to be tested on the system, using a custom cryptographic device over an already built smart card gives the opportunity to do any modification. As explained in the introduction, the scope of our project was to do research on software based encryption. Therefore the cryptographic device was built using a microcontroller. Due to the availability of devices such as programmers and also compilers with us PIC microcontrollers by Microchip company was decided to be used.

First a low cost 8 bit P16F877A PIC microcontroller which had 368 bytes of RAM was selected for the purpose. An Aptinex PIC programmer that can be connected to a computer via the USB interface was used for programming the PIC and Figure 3.1 is a photograph of that programmer. To do coding Integrated Development Environment (IDE) called mikroC by MicroElektronica was used. First, small examples were tried while implementing the circuit on a breadboard. After getting familiar with the process an AES implementation done for 8 bit PIC was obtained from [23] and changes were done according to our need. But unfortunately the RAM on the PIC P16F877A was not enough for running AES and therefore we had to go for a PIC with better specifications.

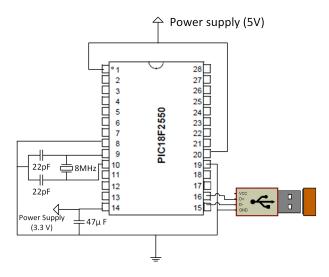

PIC18F2550 was selected as it had 2048 bytes of RAM which is a quite enough value for our purpose. Another reason that led to the selection of this PIC was the availability of an on chip

Figure 3.1: PIC programmer

USB peripheral module which would be helpful to interface with the computer to send plain text to the device. Since this PIC is going to be used throughout the project, the pin diagram of the device is shown in Figure 3.2. The AES code was compiled and the hex file was burnt to the PIC. Here the program was such that it encrypted a set of hard coded plain text using a hard coded key and then wrote the result to the EEPROM(Electrically Erasable Programmable Read Only Memory) of the PIC. The sole purpose was to verify the accuracy of the code. The circuit was setup up on a breadboard and the circuit diagram used is shown in Figure 3.3. Here the clock to the PIC has been provided via an 8MHz ceramic resonator similar to the one shown in Figure 3.4.

Then after turning on the power supply and waiting a while for the program to run, the PIC was removed and put back to the PIC programmer to read the EEPROM data. The cipher text in the EEPROM was compared with an online tool [24] that did AES encryption to verify the accuracy of the AES code we used.

Figure 3.2: Schematic diagram of PIC18F2550 from the datasheet

#### 3.1.2 USB interfacing of the PIC and encountered problems

A system that just encrypted a hard coded set of plain text is not useful and the requirement is to build a system that takes plain text from a computer, does the encryption on the device and then send back to the computer. Various possibilities to do the interfacing were inspected including parallel port, serial port and USB. Parallel port programming is easy but it is no longer found even on personal computers and hence cannot be used. Serial port is also not available on computers such as laptops and because today laptops are so widely used that option was also not a good one. In contrast USB is available on any computer and therefore we selected to use that in spite of the difficulty to program.

Figure 3.3: Most basic circuit diagram for connecting the PIC

Figure 3.4: 8MHZ resonator

USB protocol is very complicated and it requires firmware from the microcontroller side and driver from the computer side to work. Therefore writing from the scratch would be a totally different project and hence a library had to be used. MikroC has a USB library but unfortunately it was only for enumerating the device as a Human Interface Device (HID). This would be suitable for a mouse or a joystick which are common human interface devices but for our device which needed to transfer text this would not suitable. Even a software like Matlab doesnt have a API (Application Program Interface) that directly writes or reads text via such an HID interface and therefore an alternative solution had to be found.

After some investigation it was found out that the PIC C IDE by CCS had a library to enumerate a PIC as a Communication Class Device (CDC) device. This type of devices are exposed as a virtual serial port on the computer and hence programming is same as programming the serial port which is quite easy. Therefore we switched from Mikro C to PIC C. Getting familiar with PIC C which was bit different from Mikro C took some time but after a while we did necessary modifications to the code in Mikro C to make it compatible with PIC C. After verifying the accuracy of the code by an experiment similar to the one we did to Mikro C, we proceeded for USB interfacing. PIC C had easy to use library functions to handle USB and after getting familiar with them, the AES code was extended such that; it accepts plain text via USB, do the encryption and send the cipher text back to the computer. Finally it was compiled and burned to the PIC and the setup was done on a breadboard according to the circuit diagram in Figure 3.5.

Here D+ and D- in the USB port has been connected to respective pins in the PIC. Here we have designed the device as a self-powered USB device rather than a bus powered USB device. That is rather than providing power via the 5V VBUS pin in the USB port we give power using a dedicated power supply. That is why the Vcc pin of the USB port in Figure 3.5 is not connected. The reason is because USB power has lot of noise then the obtained power traces for the attack

Figure 3.5: Circuit after USB connection

would consist of noise making the attack difficult [25].

The USB device was connected to the computer but it was not even detected by the computer. By investigating a lot it was found out that USB full speed specification required a 48MHz clock while the one we used was 8MHz. It was also found out that PIC18F2550 had a Phase locked Loop (PLL) circuit that made it possible to generate a 48MHz clock signal internally using a low frequency input clock signal. This internally generated 48MHz signal can be used to provide the clock for USB. Several configuration bits had to be changed to achieve this.

After doing those changes, the device was detected by the computer but yet the "device not recognized" error came most of the times. Sometimes the device properly enumerated but still after a while, the communication froze. Again after investigating and testing out various things it was found out the culprit was the resonator we used. A resonator can have some deviation in the frequency it generates from the stated value and this small deviation affects the 48MHz signal generated by the PLL also to deviate. USB is too sensitive and such differences and such deviations cannot be tolerated. As a solution we replaced the resonator with a crystal oscillator which has a better accuracy. Figure 3.6 shows such a crystal oscillator. A crystal need two capacitors to work and hence the circuit now looks as in Figure 3.7. This circuit when connected via USB worked as expected.

Figure 3.6: 8MHz crystal

But unfortunately more problems occurred with respect to USB when introducing the power measurement resistor explained in section 3.2. When the resistor is connected serially to the device to compensate the voltage drop across the resistor, the voltage of the power supply had to be increased and when doing this suddenly the USB connection disconnected. After that it was no longer detected by the PC and after some investigation it was found out that the internal voltage regulator in the PIC that provided power for USB communication had burnt. As many users experiences in different forums said that the voltage regulator in the PIC is very sensitive

Figure 3.7: Circuit after replacing the resonator with a crystal

and burns unexpectedly, rather than buying a PIC we decided to supply a regulated 3.3V to the pin 14 of the PIC from an external supply after setting the configuration options in PIC C to turn off the internal voltage regulator.

Problems did not stop at that point where errors occurred during transmission of data. That is, data sent by the computer sometimes corrupted when being read by the PIC. Also the communication froze unexpectedly sometimes. After some investigation it was found out by putting a capacitor of value  $0.47\mu F$  to pin 14, the problem can be solved. The final circuit diagram is shown in Figure 3.8.

Figure 3.8: Circuit after settling all USB errors

#### 3.2 Power measurement circuit

The attack requires to measure the power consumed during encryption. As devices to measure power consumption of a device directly are not available, the necessity of an indirect method

arise.

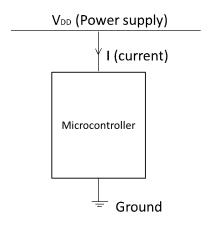

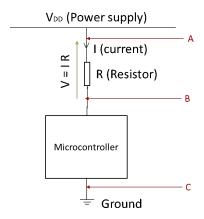

Figure 3.9 shows a simple setup of a microcontroller connected to a power supply. The power consumption is of the microcontroller at an instance is given by the equation  $p = V_{DD}I$  where I is the instantaneous current as explained section 1.4. As  $V_{DD}$  is constant, the current I is directly proportional to the power p. Therefore the power can be deduced by measuring the current. But for measuring the current a device called a current probe is needed which is costly. Therefore a method which an oscilloscope can be used is preferred but oscilloscopes measure voltage rather than current. We elaborate two techniques which make it possible for an oscilloscope to be used for measuring power.

Figure 3.9: Current drawn by a microcontroller

#### 3.2.1 Ground resistor method to measure power

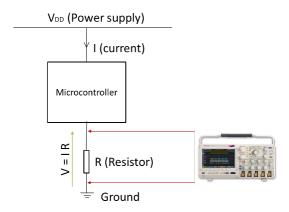

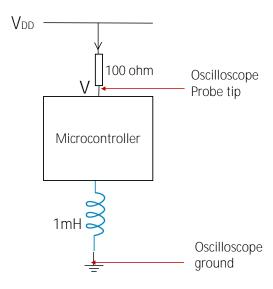

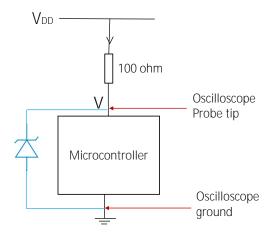

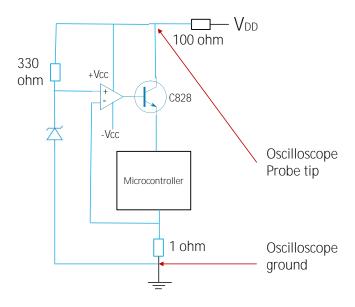

The first method is putting a resistor on the path in which the microcontroller is grounded as in Figure 3.10. Now the voltage drop across the resistor is given by V = IR where R is the resistance. As R is a constant by measuring V we can deduce I which in turn can be used to deduce the power. Therefore by connecting the oscilloscope across the resistor power can be measured as in Figure 3.10.

Figure 3.10: Measuring power using ground resistor method

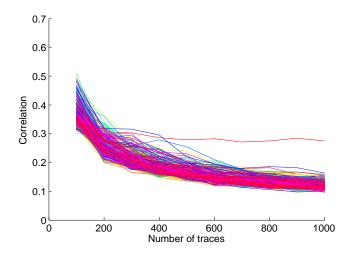

Power was captured using this method and the CPA algorithm explained in section 1.6 was run to check whether the correct key could be obtained but unfortunately it was not successful. It was found out that two factors had affected the wrongs results.

- 1. Resistance of the resistor being too small

- 2. Wrong grounding

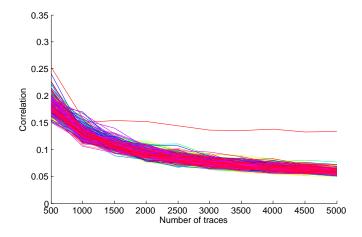

Mangard [3, pp. 49-51] in the example for his power measurement setup has used a 1 ohm resistor. But when we ran the CPA algorithm (explained in section 4.1) on the traces collected using a 1 ohm resistor we could not derive the key. But later we found out that when we used a resistor which is 10 ohms or higher we could derive the key successfully.

Figure 3.11: Wrong way to ground the oscilloscope probe

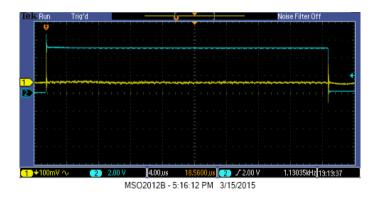

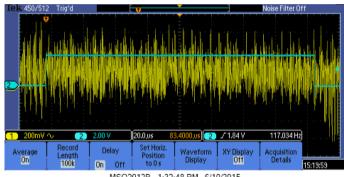

Figure 3.12: How the averaged power trace becomes 0 when oscilloscope ground is incorrectly connected

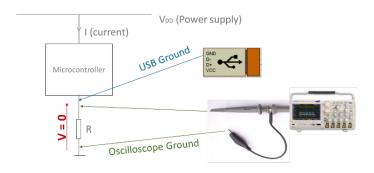

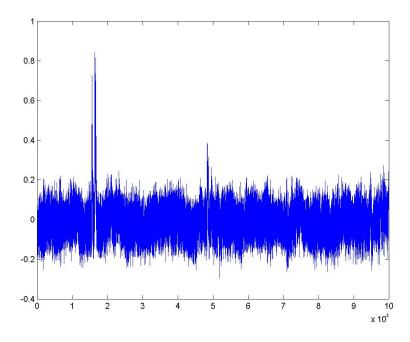

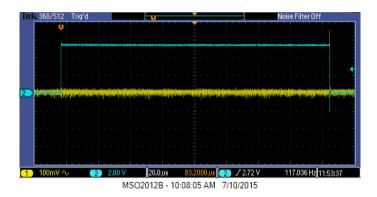

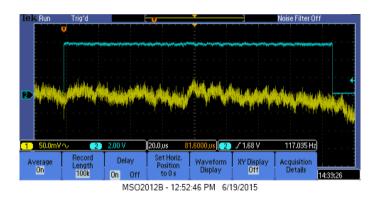

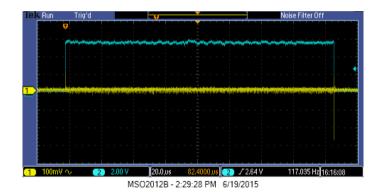

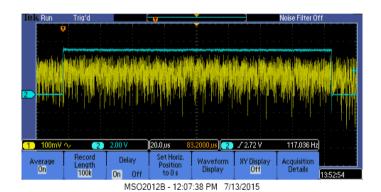

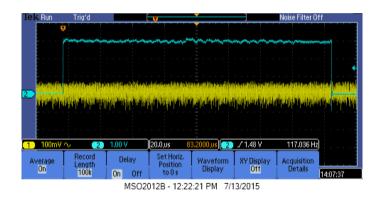

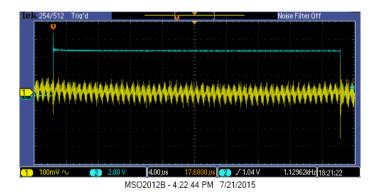

Also connecting the ground wire of the oscilloscope it must be done correctly or else the attack would not work. Initially we connected the oscilloscope probes as shown in Figure 3.11 and obtained the power traces. As the attack didnt work we took multiple power traces for the encryption of the same plain text and averaged it. This can be easily done using the functions in the oscilloscope itself. When average of multiple traces are taken the most noise cancels out and a trace that depicts an accurate power consumption can be taken [3, p. 83]. The averaged trace looked like the one shown in Figure 3.12. Here yellow wave which is almost a zero level is the power trace (voltage across the resistor) and blue wave which is a square pulse is the

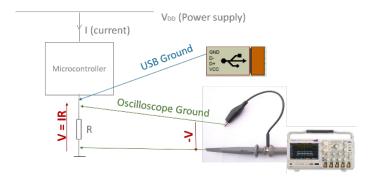

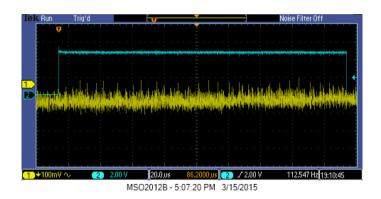

trigger used which is explained in subsection 3.2.3. As you can see, the power trace is almost 0 which means that something is wrong in the measurement. After investigation it was found out that wrong placing of ground wire of the oscilloscope was the issue. In Figure 3.11 we have connected the USB ground to the top of the resistor and the ground of the oscilloscope to the bottom of the resistor. As both ground values are the same this puts the voltage across the resistor to 0 and this explains the power trace in Figure 3.12. As a solution what we did was connecting the probe as shown in Figure 3.13. Now both grounds are connected to the same place but the power trace would be an inverted one because we are measuring a negative voltage with respect to the oscilloscope ground. But in oscilloscopes there are functions to easily invert a wave. After connecting in this correct fashion we got an average trace as shown in Figure 3.14. Now the power trace shows some significant power consumption.

Figure 3.13: Correct way to ground the oscilloscope

Figure 3.14: A good averaged power trace

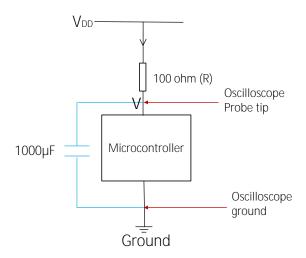

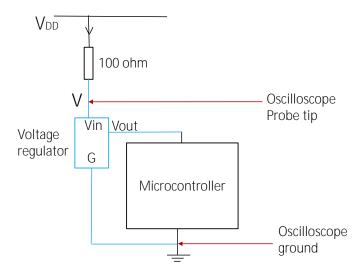

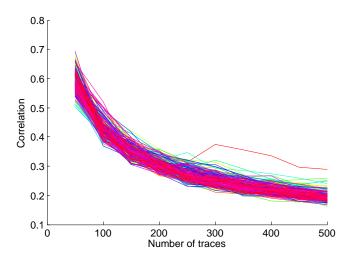

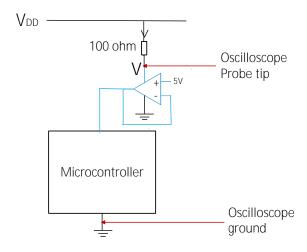

#### 3.2.2 $V_{DD}$ resistor method to measure power

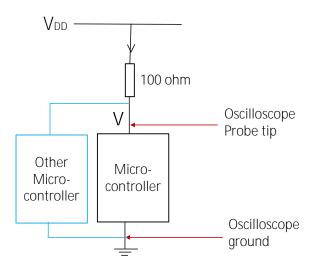

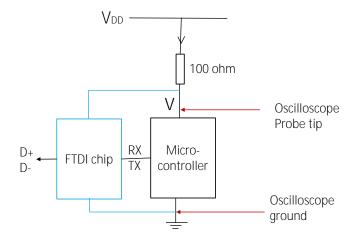

The second method is putting a resistor on the path to the power supply as shown in Figure 3.15 . The concept is similar to the previous method but now if an ordinary oscilloscope probe is connected to measure voltage across A and B in Figure 3.15 the resistor would go into flames in a few seconds just as happened to us. The reason is that when you connect the ground wire of the oscilloscope probe to B, that point is grounded and if the resistor value is small a large current will flow through it. Therefore a special probe called a differential probe which

is costly must be used to measure power across A and B. As an alternative two oscilloscope probes can be used. One oscilloscope probe can be connected to measure voltage between A and C while another probe can be connected to B and C while making sure the ground wires of both probes connect to C. Then by subtracting the voltage of the first probe by the voltage of the second probe you can get the voltage between A and B. One issue with this two probe method is the unnecessary overhead to do the subtraction of the wave forms. Another issue is most oscilloscopes usually comes with two probes and when both probes are used like this we will not have another probe to use as the trigger that is explained in subsection 3.2.3 In spite of the difficulties  $V_{DD}$  resistor method is still advantageous as elaborated in section 4.3 because it requires less number of power traces to do the attack which in turn will reduce the attack time.

Figure 3.15: Measuring power using  $V_{DD}$  resister method

Later accidentally we figured out a new interesting method where just one probe can be used to measure power using the  $V_{DD}$  resistor method. That is just by connecting the oscilloscope probe between B and C. Therefore here we measure voltage across the microcontroller rather than across the resistor. Measuring using this method lets you do the attack using lesser number of traces than what is needed when using ground resistor method. The comparison of number of traces needed is done in section 4.3.

#### 3.2.3 The trigger for the oscilloscope

Power measurement should be taken when the device is doing the encryption but not when it is idling or communicating with the computer. Therefore the oscilloscope must be properly triggered to measure the exact place we want to measure. As we made the device we have set the pin 21 of the PIC to set a signal when is starts the encryption. This signal goes to 5V when it does the encryption and when it is not it goes to 0. The blue wave form in Figure 3.12 and Figure 3.14 are the trigger signal set by pin 21. We have set the oscilloscope to trigger on the occasion when the trigger signal goes from 0 to 5V. In a situation where the cryptographic device is not programmed by the attacker yet there are methods to set the trigger but at this stage for convenience we ourselves set the trigger [3, pp. 49-51].

#### 3.3 Construction of the PCB

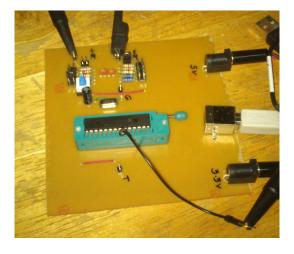

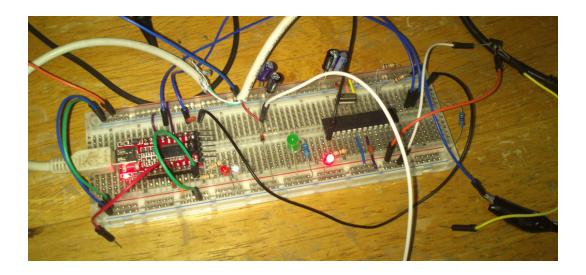

As explained in the previous sections first we tested the cryptographic device and the power measurement setup on a breadboard. The setup on the breadboard is shown in Figure 3.16. Then after fixing the issues encountered and came to a situation where the attack worked we made the setup on a dot board. On dot board we tried several attacks and as it worked we planned to create a PCB(Printed Circuit Board). The created PCB is shown in Figure 3.17. This PCB includes both power measurement methods mentioned previously where the needed one can be selected using a jumper. Also we soldered five resistors with different values for each power measurement method so that a required value can be selected for the power measurement. The advantage of having a PCB over a setup on a breadboard is that as the connections between components are much firm and as the wires going out here and there is less, the noise in the circuit is less. Therefore the number of traces needed to do an attack on the PCB is lesser than the number of traces needed to do the attack on the breadboard setup.

Figure 3.16: The cryptographic device and the power measurement setup on a breadboard

Figure 3.17: The cryptographic device and the power measurement setup on a PCB

## 3.4 Power capturing automation

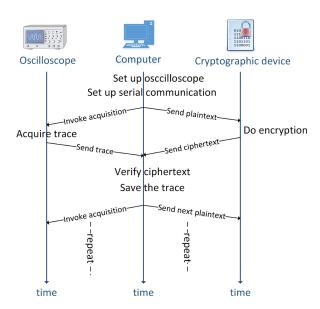

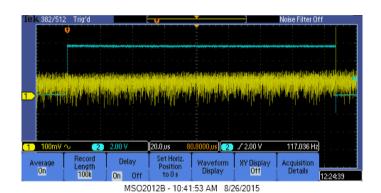

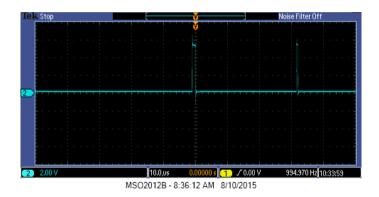

For the attack several hundred of power traces are necessary for encryption of different plain texts and obviously the capturing of all these traces cannot be done manually. Therefore some automation is required. The oscilloscope we used was Tektronix MSO2012B which had a USB interface to connect to a computer. After installing drivers the communication could be established. For the purpose of automation we selected Matlab as it had an easy to use API for handling instruments such as oscilloscopes. By doing the necessary configurations in the Instrument Toolbox in Matlab, a Matlab script was written to automatically acquire traces from the oscilloscope. This Matlab script is also responsible for sending plain text to device. As the cryptographic device has been enumerated as a USB CDC(Communication Device Class), it was also available as a virtual serial port and therefore the serial port communication functions in Matlab could be used directly. In order to check whether the communication happened correctly and the cryptographic device is working accurately after sending the plain text to the device and acquiring the power trace we acquire the cipher text from the device and compare with the same encryption done on the computer. This step was much useful to detect errors during USB communication but after getting the system working properly this step is no longer required. The overview of the basic steps in the automated power measurement setup is shown in Figure 3.18.

Figure 3.18: The overview of the basic steps in the automated power measurement setup

## 3.5 Summary

As explained above lot of difficulties arose when making the testbed and troubleshooting had to be done. Also note that explained are the significant difficulties that we faced while many other little to moderate problems that were encountered have been omitted. Therefore it is very clear that creating a testbed is a time consuming process and having an already built testbed would save a researcher interested in power analysis research from those difficulties and time consumed.

# **Chapter 4**

# **Attacking AES using CPA**

As you have understood when reading chapter 3, the creation of testbed and doing a test attack are not two isolated processes. While creating the testbed we had to do several attacks to verify whether our testbed was working properly. By doing so only we figured out errors in our setup and rectified them. To test our testbed we used AES as the algorithm under attack. The reason to select AES was because it is the most widely used block cipher in the world and therefore lot of material on how to do a power analysis on AES are available. Since people had already attacked AES we knew that if the attack does not work, the problem should be in our testbed. Otherwise if we directly started to attack an algorithm which is not yet tested we would not be able to determine whether the algorithm is not vulnerable for power analysis or whether our testbed is wrong. That is why we first tested on AES rather than directly attacking the Speck algorithm

In this chapter we first show the steps followed when attacking AES. Then we elaborate some analysis we did about power analysis using AES as the algorithm under attack.

## 4.1 Steps of the attack

#### 4.1.1 Generating plain text

We perform the attack on AES as a known plain text attack. Therefore a set of plain text samples must be generated. A C program was written to randomly generate a set of plain text. Then a set of 500 plain text samples were generated.

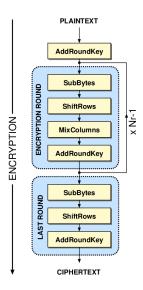

#### 4.1.2 Selection function for AES

Now a selection function must be found. The concept of the selection function for a power analysis attack was explained in section 1.6.